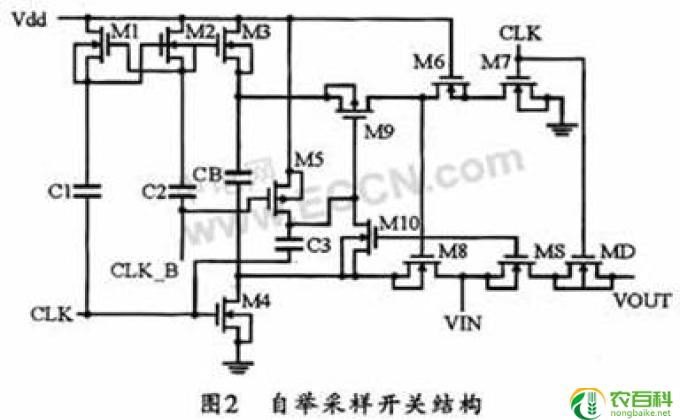

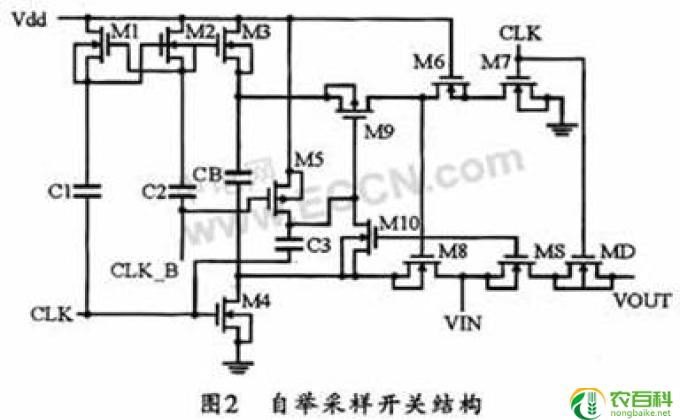

时钟(CLK)是集成电路中非常重要的一个信号。它被用来同步各个部件的操作,确保系统的正常运行。通过控制时钟信号的频率和占空比,可以精确地控制电路的操作速度和时序。

时钟(CLK)信号用来驱动各个电路元件按照特定的时间序列进行工作。它是一个周期性的信号,每个周期包含一个高电平和一个低电平。时钟的频率决定了电路的工作速度,而时钟的占空比决定了高电平和低电平的占比。

在集成电路中,时钟(CLK)的生成和分配是非常重要的。通常,一个主时钟信号会被分频、延迟、缓存等处理后再传递给各个模块和子系统。这样可以保证整个系统在统一的时钟信号下同步运行,避免数据冲突和时序错误。

时钟(CLK)信号在数字系统设计中有着重要的作用。它不仅仅是用来同步操作,还可以作为计数器的基准、数据传输的时序、电源管理的时序等等。因此,时钟设计需要考虑到系统的实际需求,并且要保证信号的稳定性和准确性。

时钟(CLK)是集成电路中用来同步各个部件操作的信号,它决定了电路的工作速度和时序。一个好的时钟设计可以提高电路的性能和稳定性,确保系统的正常运行。

-

芽插技术是一种常用的繁殖方法,适用于很多植物...

2024-01-03 06:03:06

阅读全文>>

-

选择砧木梅花砧木一般选用柿子、油橄榄、桃子等...

2024-01-03 06:03:05

阅读全文>>

-

芽插技术是一种常用的繁殖方法,适用于很多植物...

2024-01-02 21:03:08

阅读全文>>

-

选择砧木梅花砧木一般选用柿子、油橄榄、桃子等...

2024-01-02 21:03:07

阅读全文>>

-

芽插技术是一种常用的繁殖方法,适用于很多植物...

2024-01-02 16:03:12

阅读全文>>

-

选择砧木梅花砧木一般选用柿子、油橄榄、桃子等...

2024-01-02 16:03:11

阅读全文>>

-

芽插技术是一种常用的繁殖方法,适用于很多植物...

2024-01-02 11:03:07

阅读全文>>

-

选择砧木梅花砧木一般选用柿子、油橄榄、桃子等...

2024-01-02 11:03:06

阅读全文>>

-

芽插技术是一种常用的繁殖方法,适用于很多植物...

2024-01-02 06:03:09

阅读全文>>

-

选择砧木梅花砧木一般选用柿子、油橄榄、桃子等...

2024-01-02 06:03:08

阅读全文>>